# DS1747/DS1747P Y2K-Compliant, Nonvolatile Timekeeping RAMs

#### **FEATURES**

- Integrated NV SRAM, Real-Time Clock (RTC), Crystal, Power-Fail Control Circuit, and Lithium Energy Source

- Clock Registers are Accessed Identically to the Static RAM. These Registers are Resident in the Eight Top RAM Locations

- Century Byte Register (Y2K Compliant)

- Totally Nonvolatile with Over 10 Years of Operation in the Absence of Power

- BCD-Coded Century, Year, Month, Date, Day, Hours, Minutes, and Seconds with Automatic Leap Year Compensation Valid Up to the Year 2100

- Battery Voltage-Level Indicator Flag

- Power-Fail Write Protection Allows for ±10% V<sub>CC</sub> Power-Supply Tolerance

- Lithium Energy Source is Electrically Disconnected to Retain Freshness Until Power is Applied for the First Time

- DIP Module Only: Standard JEDEC Byte-Wide 512k x 8 Static RAM Pinout

- PowerCap<sup>®</sup> Module Board Only:

Surface-Mountable Package for Direct

Connection to PowerCap Containing

Battery and Crystal

Replaceable Battery (PowerCap)

Power-On Reset Output

Pin-for-Pin Compatible with Other Densities

of DS174xP Timekeeping RAM

Also Available in Industrial Temperature Range: -40°C to +85°C

PowerCap is a registered trademark of Dallas Semiconductor Corp.

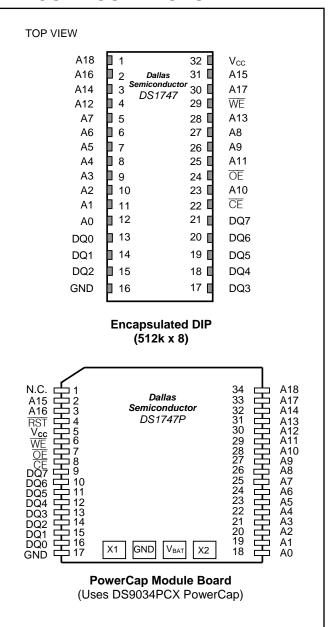

#### PIN CONFIGURATIONS

#### ORDERING INFORMATION

|                  | SUPPLY         |                                  |                  |                  |

|------------------|----------------|----------------------------------|------------------|------------------|

| PART             | <b>VOLTAGE</b> | TEMP RANGE                       | PIN-PACKAGE      | TOP MARK†        |

|                  | (V)            |                                  |                  |                  |

| DS1747-70        | 5.0            | $0^{\circ}$ C to $+70^{\circ}$ C | 32 EDIP (0.740a) | DS1747-70        |

| DS1747-70IND     | 5.0            | -40°C to $+85$ °C                | 32 EDIP (0.740a) | DS1747-70 IND    |

| DS1747P-70       | 5.0            | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*     | DS1747P-70       |

| DS1747P-70IND    | 5.0            | -40°C to $+85$ °C                | 34 PowerCap      | DS1747P-70 IND   |

| DS1747W-120      | 3.3            | $0^{\circ}$ C to $+70^{\circ}$ C | 32 EDIP (0.740a) | DS1747W-120      |

| DS1747W-120IND   | 3.3            | -40°C to +85°C                   | 32 EDIP (0.740a) | DS1747W-120 IND  |

| DS1747WP-120     | 3.3            | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*     | DS1747WP-120     |

| DS1747WP-120IND  | 3.3            | -40°C to +85°C                   | 34 PowerCap*     | DS1747WP-120 IND |

| DS1747-70+       | 5.0            | $0^{\circ}$ C to $+70^{\circ}$ C | 32 EDIP (0.740a) | DS1747-70        |

| DS1747-70IND+    | 5.0            | -40°C to $+85$ °C                | 32 EDIP (0.740a) | DS1747-70 IND    |

| DS1747P-70+      | 5.0            | 0°C to +70°C                     | 34 PowerCap*     | DS1747P-70       |

| DS1747P-70IND+   | 5.0            | -40°C to +85°C                   | 34 PowerCap*     | DS1747P-70 IND   |

| DS1747W-120+     | 3.3            | 0°C to +70°C                     | 32 EDIP (0.740a) | DS1747W-120      |

| DS1747W-120IND+  | 3.3            | -40°C to +85°C                   | 32 EDIP (0.740a) | DS1747W-120 IND  |

| DS1747WP-120+    | 3.3            | 0°C to +70°C                     | 34 PowerCap*     | DS1747WP-120     |

| DS1747WP-120IND+ | 3.3            | -40°C to +85°C                   | 34 PowerCap*     | DS1747WP-120 IND |

<sup>\*</sup>DS9034PCX, DS9034I-PCX, DS9034PCX+, DS9034I-PCX required (must be ordered separately).

#### DESCRIPTION

The DS1747 is a full-function, year-2000-compliant (Y2KC), real-time clock/calendar (RTC) and 512k x 8 nonvolatile static RAM. User access to all registers within the DS1747 is accomplished with a byte-wide interface as shown in Figure 1. The RTC information and control bits reside in the eight uppermost RAM locations. The RTC registers contain century, year, month, date, day, hours, minutes, and seconds data in 24-hour binary-coded decimal (BCD) format. Corrections for the date of each month and leap year are made automatically. The RTC clock registers are double buffered to avoid access of incorrect data that can occur during clock update cycles. The double-buffered system also prevents time loss as the timekeeping countdown continues unabated by access to time register data. The DS1747 also contains its own power-fail circuitry that deselects the device when the  $V_{\rm CC}$  supply is in an out-of-tolerance condition. This feature prevents loss of data from unpredictable system operation brought on by low  $V_{\rm CC}$  as errant access and update cycles are avoided.

<sup>†</sup>A "+" indicates a lead free. The top mark will include a "+" symbol on lead-free devices.

## **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground               | 0.3V to +6.0V                     |

|-----------------------------------------------------------|-----------------------------------|

| Operating Temperature Range (Noncondensing)               |                                   |

|                                                           |                                   |

| Storage Temperature Range                                 |                                   |

| Soldering Temperature (EDIP) (Leads, 10 seconds) (Note 7) | +260°C                            |

| Soldering Temperature (Note 7)See IPC/JEDEC Standard J-   | STD-020 for Surface-Mount Devices |

This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

## RECOMMENDED DC OPERATING CONDITIONS

$(T_A = Over the Operating Range)$

| PARAME          | TER                      | SYMBOL          | MIN  | TYP | MAX                    | UNITS | NOTES |

|-----------------|--------------------------|-----------------|------|-----|------------------------|-------|-------|

| Logic 1 Voltage | V <sub>CC</sub> = 5V±10% | $V_{ m IH}$     | 2.2  |     | $V_{CC} + 0.3V$        | V     | 1     |

| All Inputs      | $V_{CC} = 3.3V \pm 10\%$ | V <sub>IH</sub> | 2.0  |     | V <sub>CC</sub> + 0.3V | V     | 1     |

| Logic 0 Voltage | V <sub>CC</sub> = 5V±10% | $V_{ m IL}$     | -0.3 |     | +0.8                   | V     | 1     |

| All Inputs      | $V_{CC} = 3.3V \pm 10\%$ | $V_{ m IL}$     | -0.3 |     | +0.6                   | V     | 1     |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5.0V \pm 10\%, T_A = Over the Operating Range.)$

| PARAMETER                                                   | SYMBOL            | MIN  | TYP       | MAX  | UNITS | NOTES |

|-------------------------------------------------------------|-------------------|------|-----------|------|-------|-------|

| Active Supply Current                                       | Icc               |      |           | 85   | mA    | 2, 3  |

| TTL Standby Current $(\overline{CE} = V_{IH})$              | Icc <sub>1</sub>  |      |           | 6    | mA    | 2, 3  |

| CMOS Standby Current<br>$(\overline{CE} \ge V_{CC} - 0.2V)$ | Icc <sub>2</sub>  |      |           | 4    | mA    | 2, 3  |

| Input Leakage Current (Any Input)                           | $I_{IL}$          | -1   |           | +1   | μΑ    |       |

| Output Leakage Current (Any Output)                         | $I_{OL}$          | -1   |           | +1   | μΑ    |       |

| Output Logic 1 Voltage (I <sub>OUT</sub> = -1.0mA)          | $V_{\mathrm{OH}}$ | 2.4  |           |      |       | 1     |

| Output Logic 0 Voltage (I <sub>OUT</sub> = +2.1mA)          | $V_{\mathrm{OL}}$ |      |           | 0.4  |       | 1     |

| Write Protection Voltage                                    | $V_{\mathrm{PF}}$ | 4.25 |           | 4.50 | V     | 1     |

| Battery Switchover Voltage                                  | $V_{SO}$          |      | $V_{BAT}$ |      |       | 1, 4  |

## DC ELECTRICAL CHARACTERISTICS

( $V_{CC}$  = 3.3V ±10%,  $T_A$  = Over the Operating Range.)

| PARAMETER                    | SYMBOL           | MIN  | TYP               | MAX  | UNITS  | NOTES |

|------------------------------|------------------|------|-------------------|------|--------|-------|

| Active Supply Current        | Icc              |      |                   | 30   | mA     | 2, 3  |

| TTL Standby Current          | Icc <sub>1</sub> |      |                   | 2    | mA     | 2, 3  |

| $(CE = V_{IH})$              | 1001             |      |                   |      | 1111 1 | 2, 3  |

| CMOS Standby Current         | $Icc_2$          |      |                   | 2    | mA     | 2, 3  |

| $(CE \ge V_{CC} - 0.2V)$     | 1002             |      |                   |      | 1112 1 | 2, 3  |

| Input Leakage Current        | $ m I_{IL}$      | -1   |                   | +1   | μA     |       |

| (Any Input)                  | *IL              | -    |                   | . 1  | μι     |       |

| Output Leakage Current       | $I_{OL}$         | -1   |                   | +1   | μΑ     |       |

| (Any Output)                 | -OL              | -    |                   |      | μιτ    |       |

| Output Logic 1 Voltage       | $V_{ m OH}$      | 2.4  |                   |      |        | 1     |

| $(I_{OUT} = -1.0 \text{mA})$ | , OII            |      |                   |      |        | 1     |

| Output Logic 0 Voltage       | $V_{ m OL}$      |      |                   | 0.4  |        | 1     |

| $(I_{OUT} = +2.1 \text{mA})$ | V OL             |      |                   | 0.1  |        | 1     |

| Write Protection Voltage     | $ m V_{PF}$      | 2.80 |                   | 2.97 | V      | 1     |

|                              |                  |      | $V_{BAT}$         |      |        |       |

| Battery Switchover Voltage   | $ m V_{SO}$      |      | or                |      | V      | 1, 4  |

|                              |                  |      | $V_{\mathrm{PF}}$ |      |        |       |

## **AC CHARACTERISTICS—READ CYCLE (5V)**

(V<sub>CC</sub> =  $5.0V \pm 10\%$ , T<sub>A</sub> = Over the Operating Range.)

| PARAMETER                | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|-------------------|-----|-----|-----|-------|-------|

| Read Cycle Time          | $t_{RC}$          | 70  |     |     | ns    |       |

| Address Access Time      | $t_{AA}$          |     |     | 70  | ns    |       |

| CE to DQ Low-Z           | $t_{CEL}$         | 5   |     |     | ns    |       |

| CE E Access Time         | $t_{CEA}$         |     |     | 70  | ns    |       |

| CE Data Off Time         | $t_{CEZ}$         |     |     | 25  | ns    |       |

| OE to DQ Low-Z           | $t_{ m OEL}$      | 5   |     |     | ns    |       |

| OE Access Time           | $t_{OEA}$         |     |     | 35  | ns    |       |

| OE Data Off Time         | $t_{OEZ}$         |     |     | 25  | ns    |       |

| Output Hold from Address | $t_{\mathrm{OH}}$ | 5   |     |     | ns    |       |

# AC CHARACTERISTICS—READ CYCLE (3.3V)

(V<sub>CC</sub> =  $3.3V \pm 10\%$ , T<sub>A</sub> = Over the Operating Range.)

| PARAMETER                | SYMBOL          | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|-----------------|-----|-----|-----|-------|-------|

| Read Cycle Time          | $t_{RC}$        | 120 |     |     | ns    |       |

| Address Access Time      | $t_{AA}$        |     |     | 120 | ns    |       |

| CE to DQ Low-Z           | $t_{\rm CEL}$   | 5   |     |     | ns    |       |

| CE E Access Time         | $t_{CEA}$       |     |     | 120 | ns    |       |

| CE Data Off Time         | $t_{CEZ}$       |     |     | 40  | ns    |       |

| OE to DQ Low-Z           | $t_{ m OEL}$    | 5   |     |     | ns    |       |

| OE Access Time           | $t_{OEA}$       |     |     | 100 | ns    |       |

| OE Data Off Time         | $t_{OEZ}$       |     |     | 35  | ns    |       |

| Output Hold from Address | t <sub>OH</sub> | 5   |     |     | ns    |       |

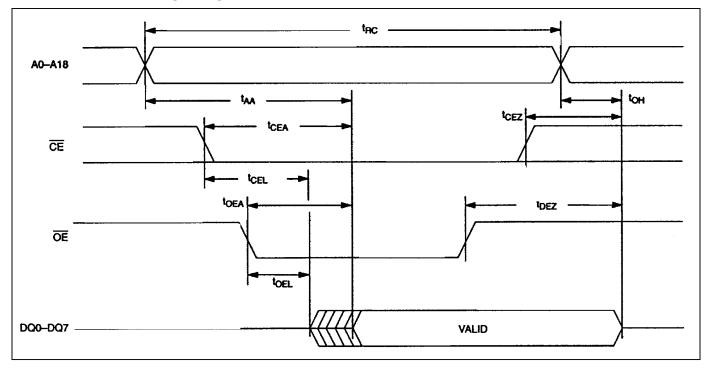

## **READ CYCLE TIMING DIAGRAM**

# **AC CHARACTERISTICS—WRITE CYCLE (5V)**

( $V_{CC}$  = 5.0V ±10%,  $T_A$  = Over the Operating Range.)

| PARAMETER           | SYMBOL             | MIN | TYP | MAX | UNITS | NOTES |

|---------------------|--------------------|-----|-----|-----|-------|-------|

| Write Cycle Time    | $t_{WC}$           | 70  |     |     | ns    |       |

| Address Setup Time  | $t_{AS}$           | 0   |     |     | ns    |       |

| WE Pulse Width      | $t_{ m WEW}$       | 50  |     |     | ns    |       |

| CE Pulse Width      | $t_{CEW}$          | 60  |     |     | ns    |       |

| Data Setup Time     | $t_{ m DS}$        | 30  |     |     | ns    |       |

| Data Hold Time      | t <sub>DH1</sub>   | 0   |     |     | ns    | 8     |

| Data Hold Time      | $t_{\mathrm{DH2}}$ | 0   |     |     | ns    | 9     |

| Address Hold Time   | $t_{ m AH1}$       | 5   |     |     | ns    | 8     |

| Address Hold Time   | $t_{ m AH2}$       | 5   |     |     | ns    | 9     |

| WE Data Off Time    | $t_{ m WEZ}$       |     |     | 25  | ns    |       |

| Write Recovery Time | $t_{WR}$           | 5   |     |     | ns    |       |

# **AC CHARACTERISTICS—WRITE CYCLE (3.3V)**

( $V_{CC}$  = 3.3V ±10%,  $T_A$  = Over the Operating Range.)

| PARAMETER              | SYMBOL             | MIN | TYP | MAX | UNITS | NOTES |

|------------------------|--------------------|-----|-----|-----|-------|-------|

| Write Cycle Time       | $t_{WC}$           | 120 |     |     | ns    |       |

| Address Setup Time     | $t_{AS}$           | 0   |     | 120 | ns    |       |

| WE Pulse Width         | $t_{ m WEW}$       | 100 |     |     | ns    |       |

| CE Pulse Width         | $t_{CEW}$          | 110 |     |     | ns    |       |

| CE and CE2 Pulse Width | $t_{CEW}$          | 110 |     |     | ns    |       |

| Data Setup Time        | $t_{ m DS}$        | 80  |     |     | ns    |       |

| Data Hold Time         | $t_{\mathrm{DH1}}$ | 0   |     |     | ns    | 8     |

| Data Hold Time         | $t_{\mathrm{DH2}}$ | 0   |     |     | ns    | 9     |

| Address Hold Time      | t <sub>AH1</sub>   | 0   |     |     | ns    | 8     |

| Address Hold Time      | t <sub>AH2</sub>   | 10  |     |     | ns    | 9     |

| WE Data Off Time       | $t_{ m WEZ}$       |     |     | 40  | ns    |       |

| Write Recovery Time    | $t_{\mathrm{WR}}$  | 10  |     |     | ns    |       |

# POWER-UP/DOWN AC CHARACTERISTICS (5V)

( $V_{CC}$  = 5.0V ±10%,  $T_A$  = Over the Operating Range.)

| PARAMETER                                                                      | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------------------------------------------------------------|-------------------|-----|-----|-----|-------|-------|

| $\overline{\text{CE}}$ or $\overline{\text{WE}}$ at $V_H$<br>Before Power-Down | $t_{\mathrm{PD}}$ | 0   |     |     | μs    |       |

| $V_{CC}$ Fall Time: $V_{PF(MAX)}$ to $V_{PF(MIN)}$                             | $t_{ m F}$        | 300 |     |     | μs    |       |

| $V_{CC}$ Fall Time: $V_{PF(MIN)}$ to $V_{SO}$                                  | $t_{ m FB}$       | 10  |     |     | μs    |       |

| $V_{CC}$ Rise Time: $V_{PF(MIN)}$ to $V_{PF}(MAX)$                             | $t_{R}$           | 0   |     |     | μs    |       |

| Power-Up Recover Time VPF to RST High (PowerCap Only)                          | t <sub>REC</sub>  |     |     | 35  | ms    |       |

| Expected Data-Retention Time (Oscillator ON)                                   | $t_{\mathrm{DR}}$ | 10  |     |     | years | 5, 6  |

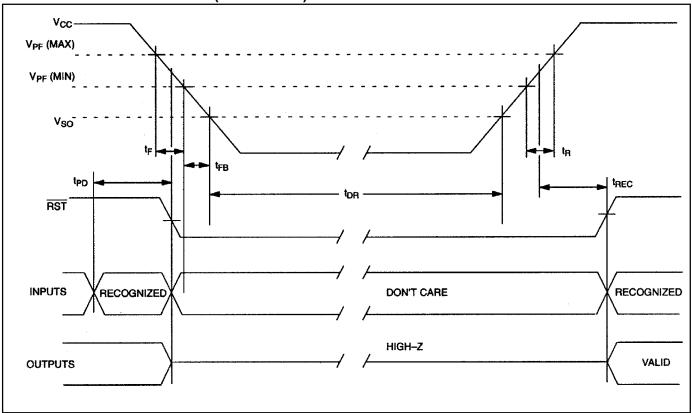

## **POWER-UP/DOWN TIMING (5V DEVICE)**

# POWER-UP/DOWN CHARACTERISTICS (3.3V)

(V<sub>CC</sub> =  $3.3V \pm 10\%$ , T<sub>A</sub> = Over the Operating Range.)

| PARAMETER                                                          | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------------------------------------------------|-------------------|-----|-----|-----|-------|-------|

| CE or WE at V <sub>H</sub> , Before Power-Down                     | t <sub>PD</sub>   | 0   |     |     | μs    |       |

| $V_{CC}$ Fall Time: $V_{PF(MAX)}$ to $V_{PF(MIN)}$                 | $t_{\mathrm{F}}$  | 300 |     |     | μs    |       |

| $V_{CC}$ Rise Time: $V_{PF(MIN)}$ to $V_{PF(MAX)}$                 | $t_R$             | 0   |     |     | μs    |       |

| Power-Up Recover Time  V <sub>PF</sub> to RST High (PowerCap Only) | $t_{ m REC}$      |     |     | 35  | ms    |       |

| Expected Data-Retention Time (Oscillator ON)                       | $t_{\mathrm{DR}}$ | 10  |     |     | years | 5, 6  |

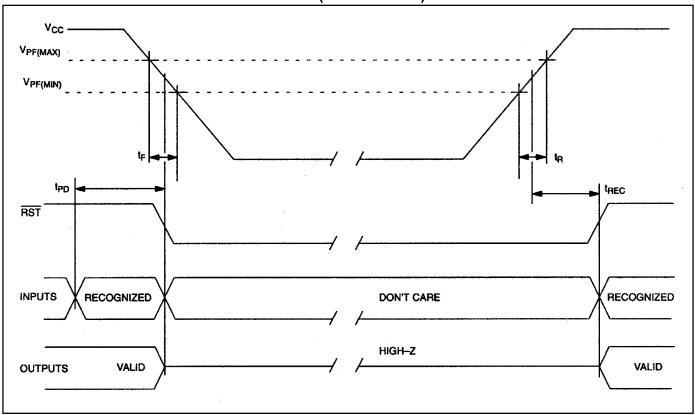

## POWER-UP/DOWN WAVEFORM TIMING (3.3V DEVICE)

#### **CAPACITANCE**

$(T_A = +25^{\circ}C)$

| PARAMETER                      | SYMBOL   | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------------|----------|-----|-----|-----|-------|-------|

| Capacitance on All Input Pins  | $C_{IN}$ |     |     | 14  | pF    |       |

| Capacitance on All Output Pins | Co       |     |     | 10  | pF    |       |

#### **AC TEST CONDITIONS**

Output Load: 50 pF + 1TTL Gate Input Pulse Levels: 0 to 3.0V

Timing Measurement Reference Levels:

Input: 1.5V Output: 1.5V

Input Pulse Rise and Fall Times: 5ns

#### **NOTES:**

- 1) Voltages are referenced to ground.

- 2) Typical values are at +25°C and nominal supplies.

- 3) Outputs are open.

- 4) Battery switchover occurs at the lower of either the battery terminal voltage or V<sub>PF</sub>.

- 5) Data-retention time is at +25°C.

- 6) Each DS1747 has a built-in switch that disconnects the lithium source until the user first applies  $V_{CC}$ . The expected  $t_{DR}$  is defined for DIP modules and assembled PowerCap modules as accumulative time in the absence of  $V_{CC}$  starting from the time power is first applied by the user.

- 7) RTC encapsulated DIP (EDIP) modules can be successfully processed through conventional wave-soldering techniques as long as temperatures as long as temperature exposure to the lithium energy source contained within does not exceed +85°C. Post-solder cleaning with water-washing techniques is acceptable, provided that ultra-sonic vibration is not used.

- 8)  $t_{AH1}$ ,  $t_{DH1}$  are measured from  $\overline{WE}$  going high.

- 9)  $t_{AH2}$ ,  $t_{DH2}$  are measured from  $\overline{CE}$  going high.